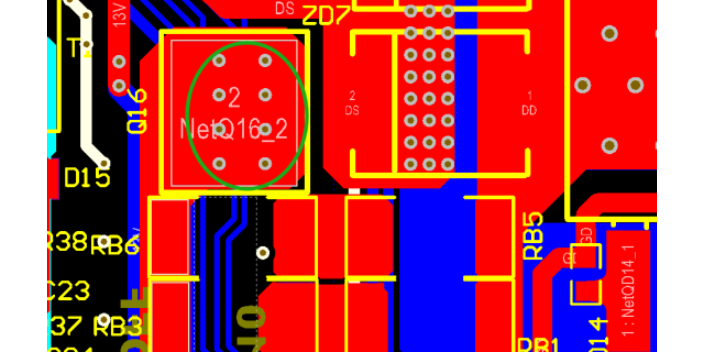

常用的拓扑结构拓扑结构是指网络中各个站点相互连接的形式。所谓“拓扑”就是把实体抽象成与其大小、形状无关的“点”,而把连接实体的线路抽象成“线”,进而以图的形式来表示这些点与线之间关系的方法,其目的在于研究这些点、线之间的相连关系。PCB设计中的拓扑,指的是芯片之间的连接关系。京晓科技可提供2-60层PCB设计服务,对HDI盲埋孔、工控医疗类、高速通讯类,消费电子类,航空航天类,电源板,射频板有丰富设计经验。阻抗设计,叠层设计,生产制造,EQ确认等问题,一对一全程服务。京晓科技致力于提供高性价比的PCB产品服务,打造从PCB设计、PCB生产到SMT贴片的一站式服务生态体。合理的PCB制板设计可以减少因故障检查和返工带来的不必要的成本。孝感焊接PCB制板走线

PCB制板表面涂层技术PCB表面涂层技术是指除阻焊涂层(和保护层)以外的用于电气连接的可焊性涂层(电镀)和保护层。按用途分类:1.焊接:因为铜的表面必须有涂层保护,否则在空气中很容易被氧化。2.连接器:电镀镍/金或化学镀镍/金(硬金,含有磷和钴)3.用于引线键合的引线键合工艺。热风整平(HASL或哈尔)热空气(230℃)压平熔融Sn/Pb焊料PCB的方法。1.基本要求:(1).锡/铅=63/37(重量比)(2)涂层厚度应至少大于3um。(3)避免因锡含量不足而形成不可焊的Cu3Sn。比如Sn/Pb合金镀层太薄,焊点由可焊的cu6sn5-cu4sn3-Cu3Sn2—-不可焊的Cu3Sn组成。2.工艺流程去除抗蚀剂-清洗板面-印刷阻焊层和字符-清洗-涂布助焊剂-热风整平-清洗。3.缺点:A.铅和锡的表面张力过大,容易形成龟背现象。B.焊盘的不平坦表面不利于SMT焊接。化学镀Ni/Au是指在PCB连接焊盘上先化学镀镍(厚度≥3um),再镀一层0.05-0.15um的薄层金或一层0.3-0.5um的厚层金。由于化学镀层均匀、共面性好,并能提供多种焊接性能,因此具有推广应用的趋势。薄镀金(0.05-0.1μm)用于保护Ni的可焊性,而厚镀金(0.3-0.5μm)用于引线键合。随州正规PCB制板批发京晓科技带您了解单层PCB制板。

PCB制板是指按照预定的设计,在共同的基材上形成点与印刷元件之间的连接的印制板。其主要职能是:1.为电路中的各种元件提供机械支撑;2.使各种电子元件形成预定电路的电气连接,起到接力传输的作用;3.用标记对已安装的部件进行标记,以便于插入、检查和调试。PCB主要应用于通讯电子、消费电子、汽车电子、工业控制、医疗、航空航天、半导体封装等领域。其中,通信、计算机、消费电子和汽车电子是下游应用占比比较高的四个领域,占比接近90%,它们的景气度直接决定了PCB行业的景气度。

PCB行业进入壁垒PCB进入壁垒主要包括资金壁垒、技术壁垒、客户认可壁垒、环境壁垒、行业认证壁垒、企业管理壁垒等。1客源壁垒:PCB对电子信息产品的性能和寿命至关重要。为了保证质量,大客户一般采取严格的“合格供应商认证制度”,并设定6-24个月的检验周期。只有验货后,他们才会下单购买。一旦形成长期稳定的合作关系,就不会轻易被替代,形成很高的客户认可度壁垒。2)资金壁垒:PCB产品生产的特点是技术复杂,生产流程长,制造工序多,需要PCB制造企业投入大量资金采购不同种类的生产设备,提供很好的检测设备。PCB设备大多价格昂贵,设备的单位投资都在百万元以上,所以整体投资额巨大。3)技术壁垒:PCB制造属于技术密集型,其技术壁垒体现在以下几个方面:一是PCB行业细分市场复杂,下游领域覆盖面广,产品种类繁多,定制化程度极高,要求企业具备生产各类PCB产品的能力。其次,PCB产品的制造过程中工序繁多,每个工艺参数的设定要求都非常严格,工序复杂且跨学科,要求PCB制造企业在每个工序和领域都有很强的工艺水平。PCB制板技术工艺哪家好?

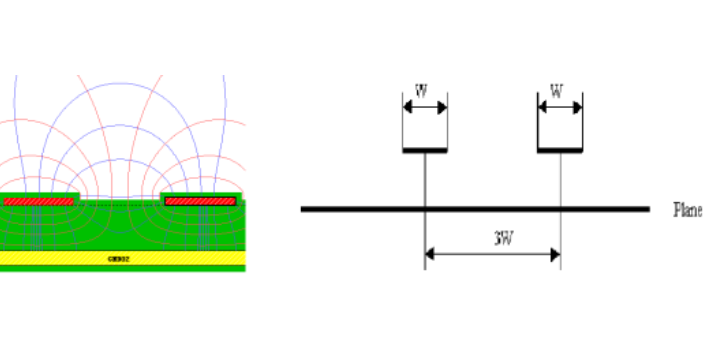

PCB制板EMI设计PCB设计中很常见的问题是信号线与地或电源交叉,产生EMI。为了避免这个EMI问题,我们来介绍一下PCB设计中EMI设计的标准步骤。1.集成电路的电源处理确保每个IC的电源引脚都有一个0.1μf的去耦电容,对于BGA芯片,BGA的四个角分别有8个0.1μF和0.01μF的电容。特别注意在接线电源中添加滤波电容器,如VTT。这不仅对稳定性有影响,对EMI也有很大影响。一般去耦电容还是需要遵循芯片厂商的要求。2.时钟线的处理1.建议先走时钟线。2.对于频率大于或等于66M的时钟线,每个过孔的数量不超过2个,平均不超过1.5个。3.对于频率小于66M的时钟线,每个过孔的数量不超过3个,平均不超过2.5个。4.对于长度超过12英寸的时钟线,如果频率大于20M,过孔的数量不得超过2个。5.如果时钟线有过孔,在过孔附近的第二层(接地层)和第三层(电源层)之间增加一个旁路电容,如图2.5-1所示,保证时钟线改变后参考层(相邻层)中高频电流的回路的连续性。旁路电容所在的电源层必须是过孔经过的电源层,并且尽可能靠近过孔,旁路电容与过孔的距离不超过300MIL。6.原则上所有时钟线都不能跨岛(跨分区)。京晓科技PCB制板其原理、工艺流程具体是什么?襄阳了解PCB制板原理

PCB设计中的拓扑是指芯片之间的连接关系。孝感焊接PCB制板走线

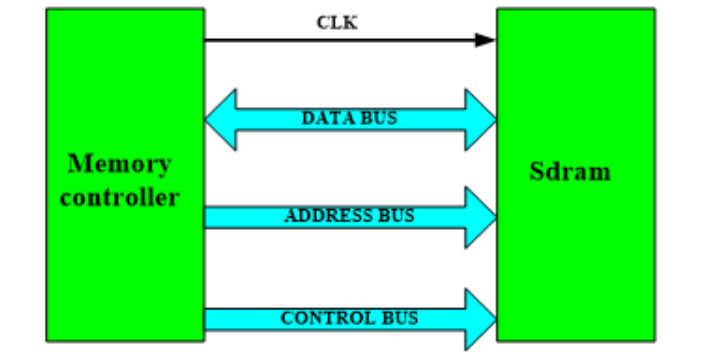

SDRAM时钟源同步和外同步1、源同步:是指时钟与数据同时在两个芯片之间间传输,不需要外部时钟源来给SDRAM提供时钟,CLK由SDRAM控制芯片(如CPU)输出,数据总线、地址总线、控制总线信号由CLK来触发和锁存,CLK必须与数据总线、地址总线、控制总线信号满足一定的时序匹配关系才能保证SDRAM正常工作,即CLK必须与数据总线、地址总线、控制总线信号在PCB上满足一定的传输线长度匹配。2、外同步:由外部时钟给系统提供参考时钟,数据从发送到接收需要两个时钟,一个锁存发送数据,一个锁存接收数据,在一个时钟周期内完成,对于SDRAM及其控制芯片,参考时钟CLK1、CLK2由外部时钟驱动产生,此时CLK1、CLK2到达SDRAM及其控制芯片的延时必须满足数据总线、地址总线及控制总线信号的时序匹配要求,即CLK1、CLK2必须与数据总线、地址总线、控制总线信号在PCB上满足一定的传输线长度匹配。孝感焊接PCB制板走线